# Power-Amplifier Module With Digital Adaptive Predistortion for Cellular Phones

Shigeo Kusunoki, *Member, IEEE*, Katsuya Yamamoto, Tadanaga Hatsugai, Hiroaki Nagaoka, Kenshi Tagami, Naoto Tominaga, Kanji Osawa, Ken Tanabe, Satoshi Sakurai, *Member, IEEE*, and Tetsuya Iida

**Abstract**—This paper describes a new type of power amplifier (PA) module with a predistortion function and can be applied to N-CDMA (narrow-band CDMA system defined in IS-95B Standard) handset terminals. Distortion compensation technology to improve the efficiency of the PA is discussed quantitatively. Various parameters to be considered in designing are investigated in detail. The predistortion technology proposed is based on the lookup-table method using the input and output signal envelopes and can operate independently from the baseband block. By omitting adaptive predistortion for amplitude/phase modulation and integrating the main controlling functions on a single CMOS integrated-circuit chip, predistortion capability has been realized in a PA module. The PA module has power-added efficiency (PAE) of 48% at an output power of 27.5 dBm. This PAE is very high in comparison with that of the conventional PA module for N-CDMA.

**Index Terms**—Amplitude–amplitude modulation (AM/AM), amplitude–phase modulation (AM/PM), code division multiple access (CDMA), module, power-added efficiency (PAE), power amplifier (PA), predistortion.

## I. INTRODUCTION

CELLULAR phones are now functioning not only as conventional wireless phones but also as portable data terminals. International Mobile Telecommunication-2000 (IMT-2000), which is the next-generation mobile communication system, will be able to provide high-bit-rate data communication services such as e-mail, audio, and high-resolution still images as well as voice. Thus, the marketing strategy for new digital radio-communication apparatus should emphasize their long continuous-usage time. However, the current consumption of handset terminals is extremely high; as a result, continuous usage time or talk time is extremely degraded.

When the handset terminal transmits data, the higher the bit rate, the higher the output power, so it is important to improve the efficiency of the power amplifier (PA). Various approaches to achieving high efficiency have been proposed. In the use of QPSK modulation, the distortion inevitably produced by the PA should be as low as possible. As well known, this requirement makes it difficult to improve the power-added efficiency (PAE)

Manuscript received April 3, 2002; revised August 14, 2002.

S. Kusunoki, K. Yamamoto, T. Hatsugai, H. Nagaoka, and K. Tagami are with Sony Ericsson Mobile Communications Japan Inc., Tokyo 108-0075, Japan (e-mail: skusnoki@sonyericsson.com).

N. Tominaga is with the Taiyo Yuden Company Ltd., Gunma 370-0024, Japan.

K. Osawa, K. Tanabe, S. Sakurai, and T. Iida are with the Toshiba Corporation, Kawasaki 212-8520, Japan.

Digital Object Identifier 10.1109/TMTT.2002.805137

TABLE I

DISTORTION COMPENSATION TECHNOLOGIES

|                        | Predistortion | Feed-forward              | RF linearizer | Proposed technology |

|------------------------|---------------|---------------------------|---------------|---------------------|

| Compensation ability   | good          | good                      | poor          | good                |

| Adaptability           | need QDM *    | need error detection loop | difficult     | need comparator     |

| Efficiency improvement | yes           | no                        | yes           | yes                 |

| Size                   | large         | large                     | small         | <b>small</b>        |

| Cost                   | high          | high                      | low           | low                 |

\*QDM:Quadratic Demodulator

of the PA. Distortion compensation is useful to reduce the distortion and improve the efficiency.

Predistortion, feed-forward, and an RF linearizer are well-known technologies. In Table I, the conventional distortion-compensation technologies are compared together with the technology presented in this paper. Conventional predistortion or feed-forward technologies, which are powerful in reducing distortion, require considerable circuit area. On the other hand, an RF linearizer is often used in the monolithic microwave integrated circuit (MMIC) or PA module because of the simplicity of its configuration [1]. However, particularly when the output power is high, the RF linearizer cannot adequately compensate for distortion. Furthermore, as the RF linearizer operates independently from the PA for which distortion compensation is performed, adaptive predistortion is difficult without another controlling function. Thus, the RF linearizer cannot significantly improve PAE. We need to develop a new distortion-compensation technology that can be realized in the PA module or MMIC.

The keys to distortion-compensation technology applicable to handset terminals are powerful distortion reduction when the output power is high, the capability to improve PAE, ease of miniaturization, low-cost fabrication, and operation independent of the baseband block. Moreover, CDMA-handset terminals have to easily follow changes in the transmission power brought about by power-control operation.

Here we focus on the predistortion technology using lookup tables (LUTs) [2], [3]. This technology allows operation independent of the baseband block and simple-to-follow power-control operations. However, as the technology needs a quadratic demodulator and two analog-to-digital convertors (ADCs) for

adaptive predistortion, the circuit size is large and there is a controlling time delay due to the LUT accessing time which will degrade the effectiveness of predistortion.

This paper describes a new predistortion technology using LUTs and reports the performance of a prototype PA module with a built-in predistortion function for N-CDMA handset terminals in Japan. Here N-CDMA is defined in IS-95B standard and the transmission frequency is from 887 to 925 MHz, data modulation is OQPSK, and the chip rate is 1.2288 Mc/s. The PA module prototype has achieved a PAE of 48% at an output power of 27.5 dBm. This PAE is very high in comparison with that of a conventional PA for N-CDMA. As can be seen in Table I, this proposed technology is good for the PA of a handset terminal.

## II. PREDISTORTION PA

### A. Investigation of PAE Improvement by Applying Predistortion

For PA operation with high PAE, the specified output power of the PA should be near to saturated output power ( $P_{\text{sat}}$ ). On the other hand, when part of the signal envelope exceeds  $P_{\text{sat}}$ , clipping distortion will appear. Consequently, even when predistortion is applied, there is still a tradeoff between PAE and distortion level.

The output voltage of the PA without predistortion is represented by

$$V_o(vi) = g(vi) \cdot \exp\{j \cdot \theta(vi)\} \quad (1)$$

where  $V_o(vi)$  is output voltage,  $vi$  is the voltage input to the PA, and  $g(vi)$  and  $\theta(vi)$  represent amplitude-amplitude modulation (AM/AM) and amplitude-phase modulation (AM/PM) of the PA, respectively. The high-frequency component is ignored in (1) and the PA is assumed to be memory-less. Considering the clipping distortion, the predistorted output voltage of the PA  $V_{o,pd}(vi)$  is represented by

$$\begin{aligned} V_{o,pd}(vi) &= g\{f(vi) \cdot \exp[j \cdot \{\theta(f(vi)) - \varphi(f(vi))\}] \\ &= (g_1 \cdot vi + g_3 \cdot vi^3 + g_5 \cdot vi^5 + \dots) \\ &\quad \cdot \exp(j \cdot \theta_0) \end{aligned} \quad (2)$$

where  $g_1$  is linear gain,  $\theta_0$  is phase offset, and  $f(vi)$ ,  $\varphi(vi)$  represent predistortion functions for AM/AM and AM/PM, respectively. In (2), when clipping distortion does not appear,  $g_3, g_5, \dots$  equals 0.

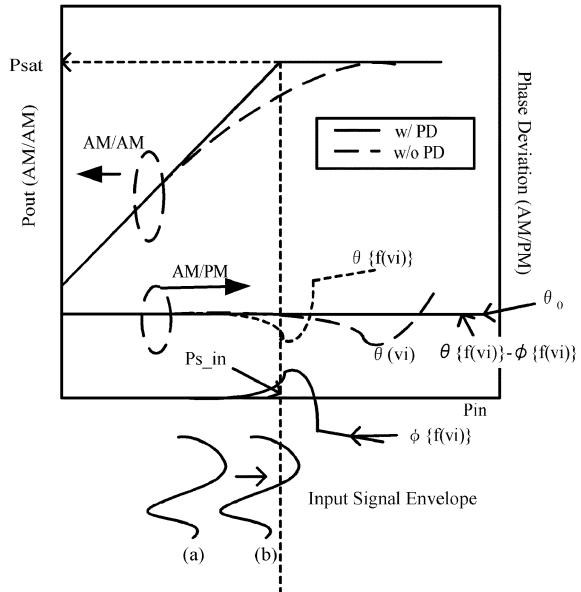

Fig. 1 shows the relation between  $\theta\{f(vi)\}$  and  $\varphi\{f(vi)\}$  in (2). Under AM/AM predistortion, AM/PM is represented not by  $\theta(vi)$  but by  $\theta\{f(vi)\}$ . So the predistortion functions of AM/PM, represented by  $\varphi\{f(vi)\}$ , should be designed to linearize  $\theta\{f(vi)\}$ .

In Fig. 1, the predistortion PA (PDPA) is linearized up to  $P_{\text{sat}}$  and the output power of the PDPA is maintained at  $P_{\text{sat}}$  in the high input-power region. When the maximum value of the input signal envelope is less than  $P_{\text{sat}}$ , as in Fig. 1(a), the output of the PDPA is linearized perfectly and there is no distortion. However, if a part of the input-signal envelope exceeds  $P_{\text{sat}}$ , as Fig. 1(b), clipping distortion will appear. This clipping distortion is represented by the  $g_3, g_5, \dots$  terms in (2). With predistortion and clipping distortion, the values of  $g_3, g_5, \dots$  are

Fig. 1. Ideal AM/AM and AM/PM characteristics of PDPA.

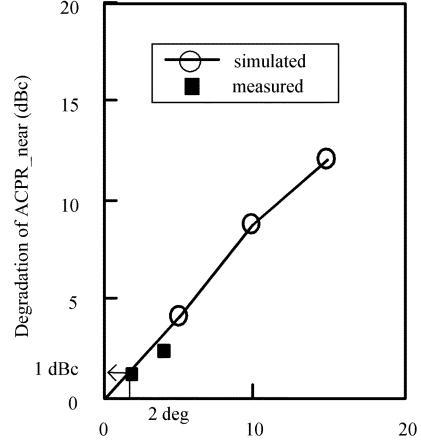

Fig. 2. Simulated and measured results of the relation between the backoff and the ACPR.

higher than without predistortion. Consequently, under predistortion, higher order distortion will be large [4]. So the difference between the specified output power and  $P_{\text{sat}}$  (this difference is called backoff) should be decided considering the specified adjacent-channel power ratio (ACPR) and the peak-to-average ratio of the modulated signal [5].

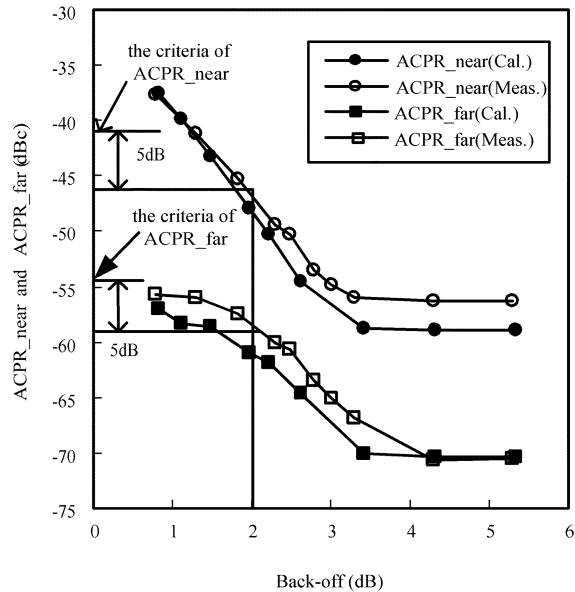

Fig. 2 shows the measured and simulated results of the relation between the backoff and the ACPR. The agreement is good. Here, (2) was used in the simulation, where  $\theta_0 = 0$ , the modulated signal is for N-CDMA, and the peak-to-average ratio is set to 5 dB. In Fig. 2, increasing the backoff decreases the ACPR. Clipping distortion will almost disappear in the region of more

Fig. 3. Block diagram of the presented PA module.

than 3 dB backoff. The value of 3 dB is decided by the probability of the appearance of the signal-envelope voltage and the peak-to-average ratio of the signal. The required backoff can be acquired from Fig. 2 by using ACPR<sub>near</sub> (= 885 kHz offset) and ACPR<sub>far</sub> (= 1.98 MHz offset) as criteria.

In Fig. 2, when both ACPR<sub>near</sub> and ACPR<sub>far</sub> are set to 5 dB lower than the specified values in IS-95B, the required backoff of 2 dB is obtained. In the case of a conventional PA for N-CDMA, as the backoff is set to 3.5–4 dB, we found that PAE is significantly improved by predistortion.

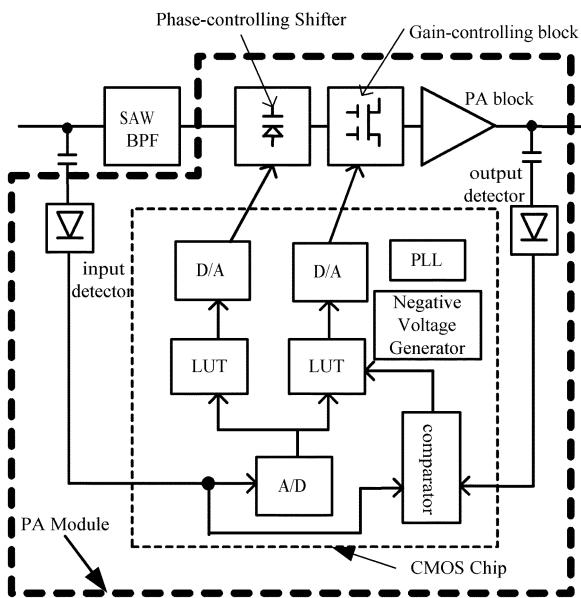

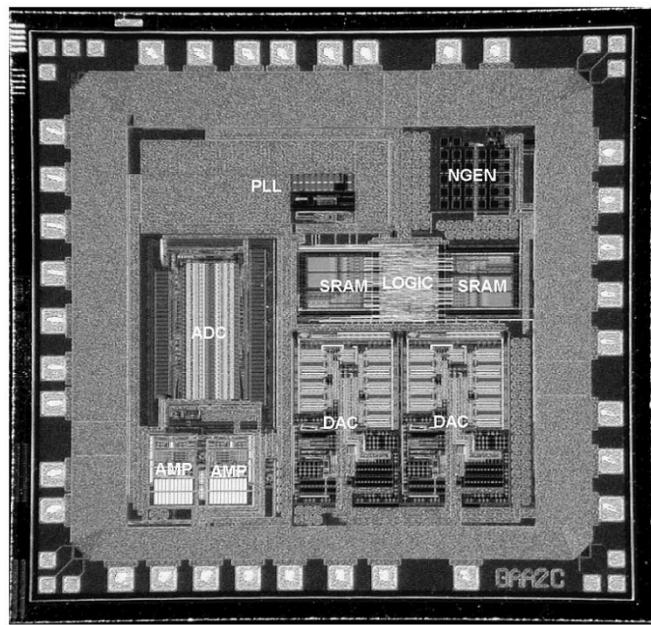

### B. Architecture

Fig. 3 shows a simple block diagram of the proposed PDPA module. It includes a PA block for which distortion compensation is performed, a gain-controlling block, a phase-controlling block, two signal-envelope detecting blocks, and a CMOS integrated circuit (IC), which controls these blocks, all packaged in one module. The CMOS IC includes an ADC, two SRAMs as LUTs, two digital-to-analog convertors (DACs), a comparator, a phase-locked loop (PLL) block, and other controlling logic. The CMOS IC also includes a negative-voltage generation block to supply negative bias voltage when depletion-mode GaAs FETs are used. Its output voltage is continuously variable from 0 to  $-1$  V.

Part of the RF input signal is detected, its variable envelope is sampled and digitized by the ADC, and the output of the ADC accesses the two LUTs. Data from the LUTs are converted to analog and drive the gain and phase controlling blocks. The two LUTs are for AM/AM and AM/PM and predistortion data is stored. For adaptive predistortion, a comparator is used for detecting the sign of the difference between the input and output signal envelopes instead of the ADC and modifies the AM/AM LUT.

The key points in the design of the gain-controlling block are the output power that can drive the following PA block up to

$P_{\text{sat}}$ , low current consumption, a wide variable range of gain, and a constant AM/PM characteristic. It is difficult to realize circuitry which satisfies all of these key points. In the proposed PDPA module, a dual-gate FET (MOS) is used. The dual-gate FET can easily vary the gain by controlling its second gate voltage. However, at the same time, the transmission phase (= phase of  $S21$ ) also varies [6]. By producing appropriate AM/PM predistortion data including the phase characteristics of the dual-gate FET and the following PA block, the total AM/PM can be linearized.

Here,  $vca$  and  $vcp$  are defined as data for AM/AM and AM/PM predistortion, respectively. Representing AM/AM and AM/PM of the dual-gate FET as  $h(vi, vca)$  and  $\theta_g(vi, vca)$ , respectively, and the phase shift of the phase-controlling block as  $ph(vcp)$ , when predistortion is performed,  $vca$  and  $vcp$  can be determined from following relations:

$$f(vi) = h(vi, vca) \quad (3)$$

$$ph(vcp) = -[\theta\{f(vi)\} + \theta_g(vi, vca)]. \quad (4)$$

The procedure of obtaining  $vca$  and  $vcp$  is as follows. First, the functions of  $h(vi, vc\_swp)$  and  $\theta_g(vi, vc\_swp)$  are obtained using a single-frequency input power sweep measurement by the vector network analyzer (VNA) by adjusting the control voltage (=  $vc\_swp$ ) applied to the second gate terminal of the dual-gate FET. Second, the AM/AM curve of the PA block for which predistortion is performed, represented by  $g(vi)$  in (1), is also obtained by power sweep measurement. The AM/AM predistortion function  $f(vi)$  can be determined from (2), where  $g3, g5, \dots$  are set to 0. Using these results in (3),  $vca$  is obtained. Third, the AM/PM curve  $[\theta\{f(vi)\} + \theta_g(vi, vca)]$  is also obtained by power sweep measurement under the AM/AM predistortion with  $vca$ . Here, as  $\theta(vi) \neq \theta\{f(vi)\}$  and the AM/AM and AM/PM predistortion are performed simultaneously, the measurement of the AM/PM curve must be performed under AM/AM predistortion. Inverting the sign of the measured result  $[\theta\{f(vi)\} + \theta_g(vi, vca)]$  and using (4),  $vcp$  can be obtained.  $vca$  and  $vcp$  are stored in the LUTs as data for predistortion.

From (3),  $vca$  is solved as a function of variable  $vi$ , and, substituting this result into (4),  $vcp$  can also be solved as a function of variable  $vi$ . Thus, both  $vca$  and  $vcp$  can be decided as functions of variable  $vi$ .

## III. ADAPTIVE PREDISTORTION

### A. Adaptive Predistortion for AM/PM

The characteristics of semiconductor devices utilized in handset terminals are affected by environmental parameters, for example, temperature and supply voltage. The CPU in the handset terminal has to modify several controlling signals for the fluctuation of environmental parameters. For example, offset-gain data is stored in data tables. In the case of the proposed PDPA, for predictable fluctuations, LUTs are modified beforehand. But, for unpredictable fluctuation, adaptive predistortion technology is needed.

In well-known adaptive predistortion technologies, a demodulator circuit is used to detect the distortion resulting from AM/PM nonlinearity [2], [3]. However, as the demodulator

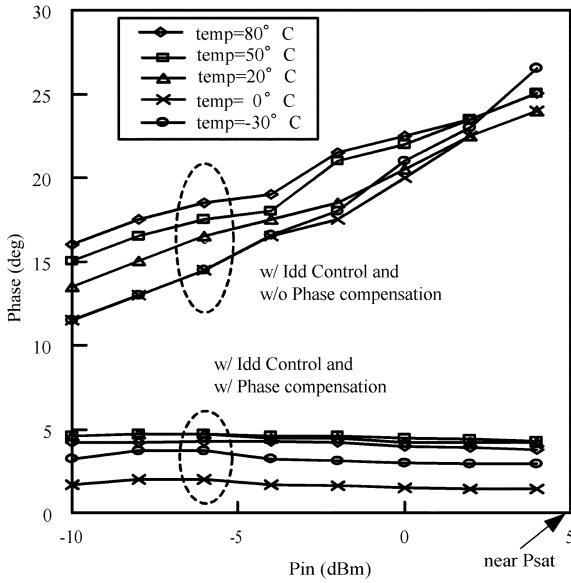

Fig. 4. AM/PM temperature dependence, with and without AM/PM predistortion, under the constant  $I_{dd}$ .

circuit occupies a large space, it is not acceptable for the PDPA module where size is critical.

In the proposed PDPA, the adaptive predistortion for AM/PM is omitted. The reason is explained below.

Because the supply voltage fluctuates between 3.5–4.0 V, the dependence on the supply voltage of the PA block is small. The most important environmental parameter here is temperature.

The AM/PM nonlinearity is represented by the relation between nonlinear parasitic capacitances  $C_{gs}$ ,  $C_{gd}$ ,  $C_{ds}$  and other nonlinear parameters in the GaAs FET [7]. Several simulation models of these nonlinear parameters depending on temperature have been proposed [8]. However, few of these models represent the characteristic of the AM/PM depending on temperature precisely, including the saturated region. We measured the temperature dependence of the AM/PM.

There is such a case that, when the temperature changes, the AM/PM, represented by  $\theta(v_i)$  in (1), does not change except for [9]. This is remarkable when the drain current is constant by controlling the gate bias voltage.

Fig. 4 shows the measured results of two cases of AM/PM temperature dependence, with AM/PM predistortion and without, under constant drain current. As can be seen in Fig. 4, the AM/PM for different temperatures is maintained to be almost constant with constant drain current. Moreover, performing predistortion for AM/PM, phase deviation is maintained at less than 2°. Fig. 5 shows measured and simulated results of the remaining ACPR\_near due to irregularities in the AM/PM predistortion. In Fig. 5, the measured result is obtained by measuring the ACPR of some PA modules whose AM/PM is different from each other. In the measurement, only AM/AM predistortion is performed to avoid the effect of amplitude distortion. From Figs. 4 and 5, if the remaining phase deviation is less than 2°, it is expected that the degradation of ACPR\_near is less than 1 dB. Consequently, this degree of degradation of

Fig. 5. Measured and simulated results of the remaining ACPR\_near due to irregular AM/PM predistortion.

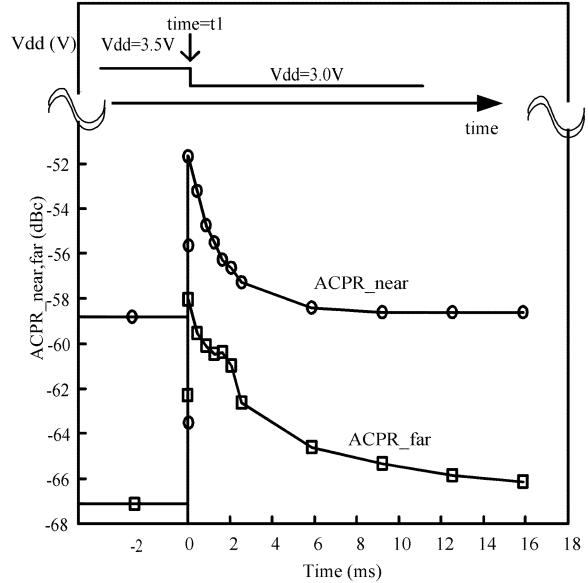

Fig. 6. Simulated result of convergence time to modify the AM/AM LUT by the adaptive predistortion when the supply voltage stepped down from 3.5 V to 3.0 V at time =  $t_1$ .

ACPR is not important when the adaptive predistortion for AM/PM is omitted.

#### B. Adaptive Predistortion for AM/AM

In the case of adaptive predistortion for AM/AM, an ADC is often used to detect the output signal envelope. The ADC can be integrated in the CMOS IC, but it occupies a large space and also requires a large current. So, as noted above, in the proposed PDPA, a comparator is used.

Fig. 6 shows the simulated result of convergence time to modify the AM/AM LUT by adaptive predistortion. The simulation condition is that the predistortion is performed perfectly until time =  $t_1$ , and at time =  $t_1$  the supply voltage to the PA steps down from  $V_{dd} = 3.5$  V to  $V_{dd} = 3.0$  V. As the data in AM/AM LUT does not apply for  $V_{dd} = 3.0$  V, adaptive

predistortion must modify the data in AM/AM LUT. As can be seen in Fig. 6, the ACPR decreases gradually with modification of the data in LUT, and it takes about 3 ms to make the modification. The dominant factor of the convergence time is regarded as the probability of the appearance of signal-envelope voltage. In Fig. 6, ACPR\_far is going to decrease in the region of more than 3 ms. This is considered to be so because the memory cells in the LUT corresponding to the low-probability signal-envelope voltage cannot be modified frequently, so unapplicable data remain for a long period. In fact, as both voltage and temperature fluctuate slowly, a convergence time of the order of 3 ms is not important.

#### IV. DESIGN AND PERFORMANCE

##### A. Design of PDPA

From simulation, the required variable range of the gain-controlling block was found to be more than 4.5 dB. Furthermore, fluctuations due to adaptive predistortion and constant deviation of the devices have to be considered. As noted above, a dual-gate FET was used for the gain-controlling block, and a variable gain range of more than 10 dB was achieved by varying the voltage on the second gate terminal in a 1.5-V range.

In the phase-controlling block, a variable-capacitance diode was used. Its phase-controlling range was more than  $10^\circ$ .

As noted above, the keys of designing a PA block appropriate for predistortion are  $P_{\text{sat}}$  and PAE at the specified output power. From simulated results, the required  $P_{\text{sat}}$  was  $P_{\text{sat}} > 29.3 \text{ dBm}$ , so the design target was set to 30 dBm. The matching circuit was designed to be memory-less. The PAE should be as high as possible at the specified output power. The PAE of the PA block was 51% at  $P_{\text{out}} = 27.5 \text{ dBm}$ .

The data for LUTs are stored in a flush RAM for controlling data in a handset terminal and down-loaded to the LUTs when the main power is on or when necessary.

The distortion compensation is shut down when the output power is low because distortion is not a dominant factor in restraint of the PAE. In this shut-down mode, the supply voltage to CMOS IC is shut off, but the output of the DACs is maintained at a constant voltage so there is no discontinuity of gain between ON and OFF.

##### B. Delay Time Sensitivity

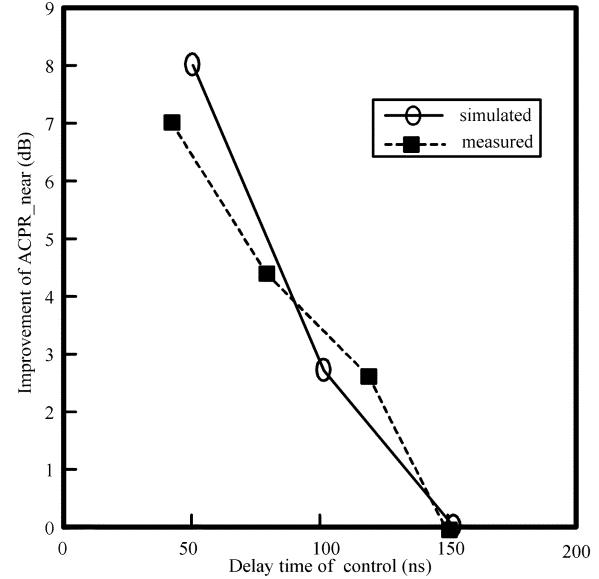

In the proposed PDPA, distortion compensation is sensitive to the time delay of the CMOS IC. Fig. 7 shows the measured and simulated results of ACPR\_near degradation due to the delay time. Fig. 7 shows that improvement of ACPR\_near is degraded as the delay time increases. In Fig. 7, it is seen that the allowable delay time is determined by

$$\tau_{da} < \frac{1}{40} \cdot f_{\text{max}}. \quad (5)$$

Here,  $f_{\text{max}}$  is the maximum frequency of the signal envelope and  $f_{\text{max}} = 614.4 \text{ kHz} (= 1.2288 \text{ MHz}/2)$  for N-CDMA. Then, from (5),  $\tau_{da} < 40 \text{ ns}$ .

To minimize the delay time, a flush-type ADC and the  $0.25\text{-}\mu\text{m}$  process are used in CMOS IC. It takes 25 ns from A/D start to D/A output. Considering application to a high

Fig. 7. Measured and simulated results of ACPR\_near degradation due to the delay time.

Fig. 8. ACPR and PAE performance of the proposed PDPA module.

signal envelope frequency system, for example, W-CDMA, part of the RF signal is detected before the RF-SAW bandpass filter (BPF), as shown in Fig. 1. As the group delay of the SAW BPF is about 30 ns, the delay of the CMOS IC can be mostly cancelled.

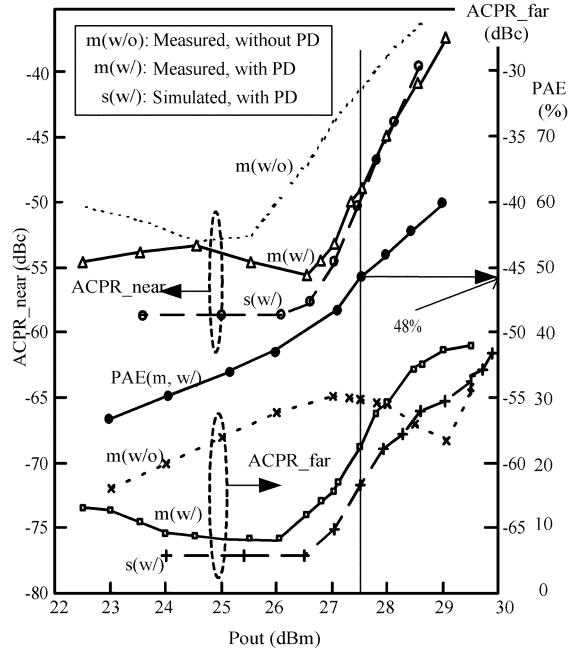

##### C. Performance

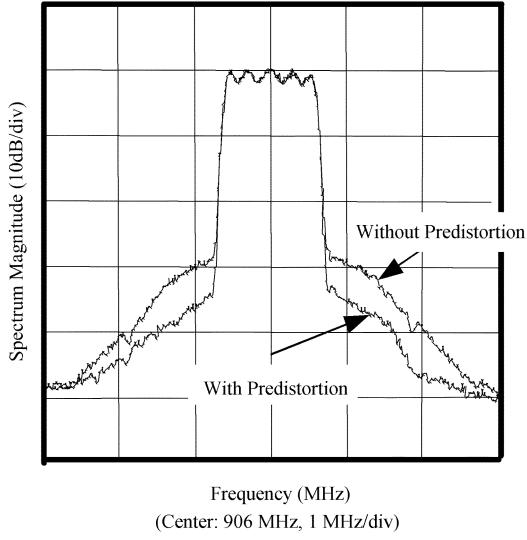

Fig. 8 shows the ACPR and PAE performance of the proposed PDPA module. Fig. 9 shows the output spectrum of the module when  $P_{\text{out}} = 27.5 \text{ dBm}$ . The RF signal is for N-CDMA

Fig. 9. Output spectrum of the proposed PA module with and without predistortion.

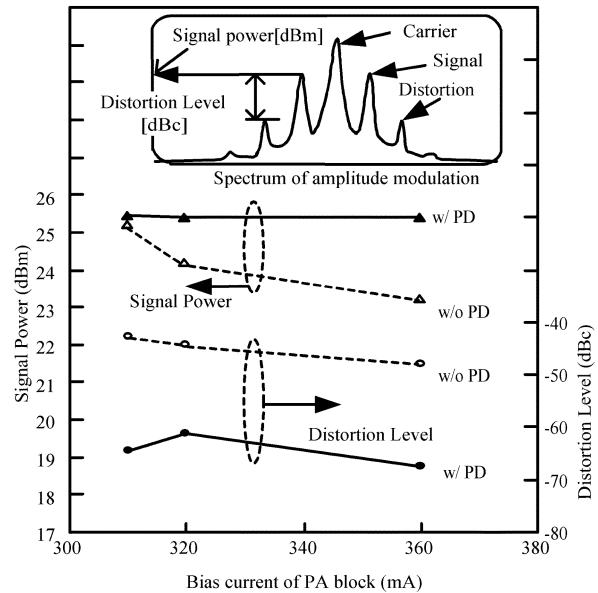

Fig. 11. Comparison of signal-power and distortion-level variation effect on the bias current of the PA.

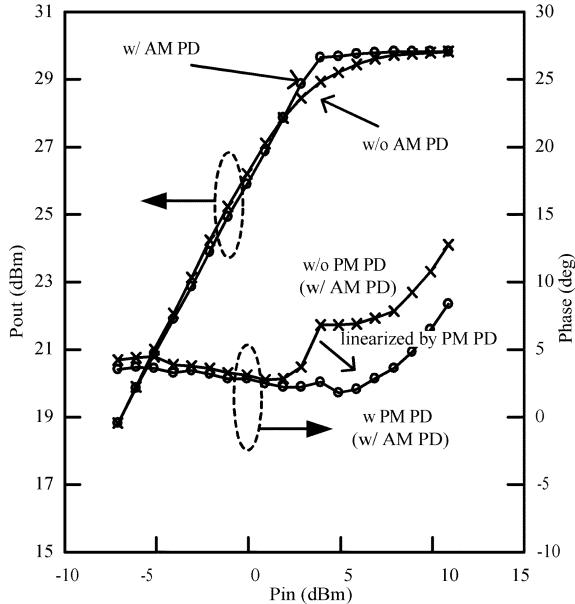

Fig. 10. Performance of gain and phase linearization.

in Japan. From Fig. 8,  $ACPR_{near} = -49$  dBc (7 dB improvement) and  $ACPR_{far} = -59$  dBc (4 dB improvement) were achieved at the output power of 27.5 dBm. The PAE was 48%, including the current consumption of the CMOS IC and the gain-controlling block. The CMOS IC consumed about 15 mA. As the PAE of the conventional PA for N-CDMA is about 40% at most, the 48% of the PAE is high. If F-class technology is applied to the PA, there will be a further improvement of the PAE. In Fig. 8, the simulated results of  $ACPR_{near}$  and  $ACPR_{far}$  with predistortion are also shown. The agreement is good. In Fig. 8,  $ACPR_{near}$  and  $ACPR_{far}$  increase rapidly when the

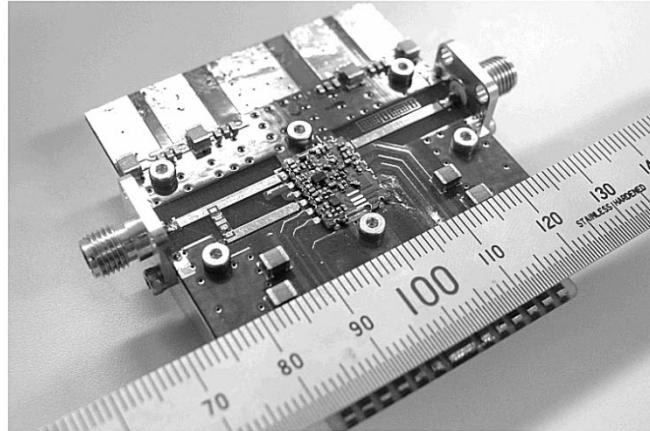

Fig. 12. Prototype of the PDPA module mounted on an evaluation board.

output power is more than  $P_{out} = 26$  dBm or 26.5 dBm. This rapid increase is due to the signal envelope clipping by  $P_{sat}$ .

The receiver band noise level was  $-138$  dBm/Hz. Here, the receiver band is from 832 to 870 MHz.

In Fig. 10, the AM/AM and AM/PM schemes with and without predistortion are shown. In the AM/AM scheme, we see that the nonlinearities, including that of the dual-gate FET, are also linearized. The AM/PM without phase predistortion (w/o PMPD and w/ AMPD) represents large phase deviation between  $P_{in} = 2$  dBm and 3 dBm. This characteristic due to the AM/AM, that is  $\theta\{f(vi)\}$ , is shown in Fig. 10 as linearized.

For the examination of adaptive predistortion, measurements of the signal and distortion level using an amplitude-modulated signal whose peak-to-average power ratio is 1.5 dB, with bias current variation, was performed. The bias current often varies with environmental parameters, particularly temperature. The measured results are shown in Fig. 11. As shown in Fig. 11, the AM signal is composed of a carrier component, two signal

Fig. 13. Photograph of the CMOS IC chip.

components, and two distortion components. When there is distortion, the signal-component level decreases and the distortion-component level increases. In Fig. 11, the signal power is constant with the adaptive predistortion, i.e., recovery of the signal envelope is performed. The improvement of distortion is maintained at less than 10 dB, compared with the PA without adaptive predistortion. This means that the distortion compensation except for AM/PM adaptive predistortion operates effectively, even when the bias current varies.

Fig. 12 is a photograph of the prototype of the proposed PDPA module mounted on an evaluation board. The proposed PDPA module is 11 mm × 10 mm × 2 mm, made possible by mounting the CMOS IC chip and the GaAs FET chips on the backside of the module. Such a size is sufficiently small to allow utilization in a cellular phone. The size could be even smaller if an MMIC-PA chip integrated with the dual-gate FET is used. Fig. 13 is a photograph of the CMOS IC, whose size is 2.5 × 2.5 mm.

## V. CONCLUSION

A new type of PDPA module for handset terminals has been implemented. The predistortion technology is based on the LUT method using the input and output signal. A CMOS IC chip using the 0.25- $\mu$ m process is developed for quick control of predistortion and for miniaturization of the PDPA. The PDPA module includes an adaptive predistortion function for AM/AM to compensate for environmental fluctuations. An adaptive predistortion function for AM/PM is omitted. By integrating all functions on one module, a PDPA module applicable to handset terminals is developed without degrading the distortion-compensation capability. The PAE of this PDPA is achieved 48% at an output power of 27.5 dBm. This PAE is very high in comparison with that of the conventional PA for N-CDMA.

## ACKNOWLEDGMENT

The authors thank M. Komatsubara, H. Usui, N. Watanabe, K. Takagi, and N. Sato, all of Sony Ericsson Mobile Communications Japan, Tokyo, Japan, for their support of this work.

## REFERENCES

- [1] G. Hau, T. Nishimura, and N. Iwata, "A highly efficient linearized wide-band CDMA handset power amplifier based on predistortion under various bias conditions," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1194–1201, June 2001.

- [2] E. G. Jeckeln, F. Beauregard, M. A. Sawan, and F. M. Ghannouch, "Adaptive baseband/RF predistorter for power amplifiers through instantaneous AM–AM and AM–PM characterization using digital receivers," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2000, TUIF-24, pp. 489–492.

- [3] P. B. Kenington, M. Cope, R. M. Bennett, and J. Bishop, "A GSM-EDGE high power amplifier utilising digital linearization," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2001, TH1D-5, pp. 1517–1520.

- [4] F. Amoroso, "Regrowth of data spectral sidelobes from AM/PM effects and hard limiting," *Microwave J.*, pp. 148–154, Oct. 2001.

- [5] J. F. Sevic and M. B. Steer, "On the significance of envelope peak-to-average ratio for estimating the spectral regrowth of an RF/microwave power amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 1068–1071, June 2000.

- [6] H. Hayashi and M. Muraguchi, "An MMIC variable-gain amplifier using a cascode-connected FET with constant phase deviation," *IEICE Trans. Electron.*, vol. E81-C, no. 1, pp. 70–77, Jan. 1998.

- [7] H. A. Jardon and H. L. Vazquez, "A novel presentation of AM–PM conversion," in *Int. Electromagn. Compat. Rec. Symp.*, 1995, pp. 401–405.

- [8] J. Rodriguez-Tellez, B. P. Stothard, and C. Galvan, "Comparison of temperature models for the drain current of MESFET's," *IEEE Trans. Computer-Aided Design*, vol. 15, pp. 968–976, Aug. 1996.

- [9] H. Q. He and M. Faulkner, "Performance of adaptive predistortion with temperature in RF power amplifier linearization," in *Proc. ISSPA '99*, pp. 717–720.

**Shigeo Kusunoki** (M'02) received the B.E. and M.E. degrees in electronic engineering from the University of Electro-communications, Tokyo, Japan, in 1979 and 1981, respectively.

In 1981, he joined the NEC Corporation. In 1991, he joined the Sony Corporation. Since then, he has been with the Sony Research Center and the Semiconductor Industrial Departments. He has been engaged in the research and development of GaAs MMIC. He is currently with Sony Ericsson Mobile Communications Japan Inc., Tokyo, Japan.

Mr. Kusunoki is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Katsuya Yamamoto** received the B.S. degree in electronics engineering from the University of Tokyo, Tokyo, Japan, in 1987.

In 1991, he joined the Sony Corporation. Since then, he has been with the Telecommunication and Information System Research Laboratory and the Personal Telecommunications Departments. He has been engaged in research and development of CDMA handset terminal and communication system. He is currently with Sony Ericsson Mobile Communications Japan Inc., Tokyo, Japan.

**Tadanaga Hatsugai** received the M.E. degree in electronics and mechanical science from Chiba University, Chiba, Japan, in 1999.

In 1999, he joined the Sony Corporation. He is currently with Sony Ericsson Mobile Communications Japan Inc., Tokyo, Japan. He has been engaged in research and development of high-efficiency PAs for wireless handset terminals.

**Kanji Osawa** received the B.E. degree in electronic engineering from Tokai University, Kanagawa, Japan, in 1984.

In 1984, he joined the Semiconductor Division, Toshiba Corporation, Kawasaki, Japan. From 1984 to 1989, he was engaged in the development of mixed analog/digital CMOS system LSIs for PBX and telephony. Since 1990, he has engaged in the development of mixed analog/digital CMOS system LSI for mobile telecommunication.

**Hiroaki Nagaoka** received the M.S. degree from Saitama University, Saitama, Japan, in 2001.

In 2001, he joined the Sony Corporation. He is currently with Sony Ericsson Mobile Communications Japan Inc., Tokyo, Japan. He has been engaged in research and development of high-efficiency PAs for wireless handset terminals.

Mr. Nagaoka is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Ken Tanabe** received the B.E. degree in electronic engineering from the Tokyo Denki University, Tokyo, Japan, in 1990.

In 1990, he joined the Semiconductor Division, Toshiba Corporation, Kawasaki, Japan. Since 1990, he has engaged in the development of mixed analog digital circuit technique for CMOS LSIs for consumer and telecommunication.

Mr. Tanabe is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan.

**Kenshi Tagami** received the B.E. degree from Fukuoka University, Fukuoka, Japan, in 1991.

He then joined the Sony Corporation. He is currently with Sony Ericsson Mobile Communications Japan Inc., Tokyo, Japan. He has been engaged in the development and design of mobile telephones.

**Satoshi Sakurai** (S'90–M'90) received the B.S. and M.S. degrees in information sciences from Tohoku University, Sendai, Japan, in 1994 and 1996, respectively.

In 1996, he joined the Semiconductor Division, Toshiba Corporation, Kawasaki, Japan. He has been engaged in the development of mixed analog/digital CMOS LSIs, predominantly for consumer applications in telecommunication.

**Naoto Tominaga** received the B.E. degree from Kinki University, Osaka, Japan, in 1998.

In 1998, he joined the Taiyo Yuden Company Ltd., Gunma, Japan. He has been engaged in the research and development of the PA modules for wireless handset terminals.

**Tetsuya Iida** received the B.S. degree in electrical engineering from Tohoku University, Sendai, Japan, in 1975.

In 1975, he joined the Semiconductor Division, Toshiba Corporation, Kawasaki, Japan. From 1975 to 1977, he was engaged in the development of analog CMOS LSIs such as DTMF generator and 13-b analog-to-digital converters. From 1978 to 1984, he was engaged in the research of charge-coupled device (CCD) delay lines and transversal filters for TV. Since 1985, he has been engaged in the development of mixed analog digital circuit technique for telecommunication CMOS LSIs.